반도체 파운드리패권전쟁 가열

삼성, 내년 상반기 양산 목표

첨단기술 GAA앞세워 우위 자신

TSMC는 내년 하반기 양산 계획

2나노 양산도 2025년 시기 비슷

인텔 "2024년 2나노 양산" 밝혀

삼성, 내년 상반기 양산 목표

첨단기술 GAA앞세워 우위 자신

TSMC는 내년 하반기 양산 계획

2나노 양산도 2025년 시기 비슷

인텔 "2024년 2나노 양산" 밝혀

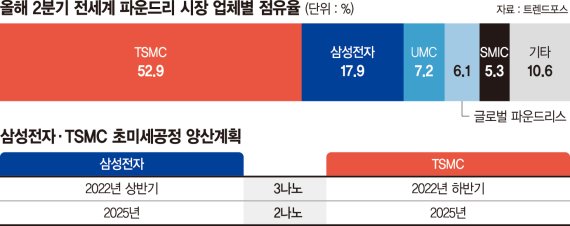

글로벌 반도체 파운드리 1·2위 업체인 TSMC와 삼성전자가 오는 2025년 2나노미터(1㎚=10억분의 1m) 공정 양산을 예고하며 초미세공정 시장 주도권을 쥐기 위한 경쟁이 가열되고 있다.

삼성전자는 3나노 공정부터 적용되는 차세대 트랜지스터 제조 기술인 GAA(게이트올어라운드) 기술력을 기반으로 3나노 이하 공정에서 TSMC를 앞선다는 구상이다.

17일 관련 업계에 따르면 TSMC는 내년 하반기 3나노, 2025년 2나노 공정 양산 계획을 발표했다. 삼성전자보다 3나노 양산은 늦고, 2나노 양산 시기는 비슷하다.

TSMC와 삼성전자 모두 2025년 2나노 양산 계획을 발표한 가운데 삼성전자는 3나노 이하 초미세공정 시장 선점에 자신감을 드러내고 있다. 3나노 공정에서 TSMC가 내년 하반기 양산 계획을 밝힌 반면 삼성전자는 내년 상반기를 목표로 하고 있다.

고객사 주문을 받아 위탁생산을 하는 파운드리 사업은 양산 시기가 빠를수록 시장 점유율 확보 및 신규 고객사 확보에 유리하다. 2나노 공정에서도 3나노 공정부터 쌓인 GAA 등 기술 노하우를 기반으로 기술 우위를 확보할 계획이다. 미국 반도체 전문지 EE타임스는 "삼성전자가 TSMC· 인텔보다 차세대 트랜지스터 기술을 가장 적극적으로 추진하고 있다"고 평가했다.

삼성전자는 내년 상반기 양산되는 3나노부터 GAA 기술을 적용하며, 2023년 3나노 2세대의 양산을 시작한다. 기존 3나노보다 성능을 대폭 끌어올린 버전이다. 삼성전자는 3나노 공정에서 안정적 수율을 확보한 것으로 알려졌다. 공정이 미세해질수록 수율 관리 난이도가 높아져 삼성전자는 2년간의 GAA 기술력을 반영해 2025년 2나노 양산에 나설 계획이다.

GAA는 전류 흐름을 조절하는 스위치 역할을 하는 반도체 트랜지스터 구조를 개선해 기존 핀펫(FinFET) 구조보다 전력 효율을 높인 기술이다. 핀펫 기반 5나노 공정 대비 성능은 30% 향상되며 전력소모는 50%, 면적은 35% 감소한다. 반면 TSMC는 3나노 공정까지 기존 핀펫 방식을 유지하고, 2나노 양산에서 GAA를 도입키로 했다.

삼성전자 관계자는 "3나노에서 충분히 기술 노하우를 쌓고 2나노로 넘어가겠다는 것으로, 2나노부터 바로 GAA를 적용하는 TSMC와는 전략적 차이가 있다"면서 "2년 가량의 GAA 노하우를 바탕으로 기술적 안정성과 경쟁력을 확보해 2나노 공정에서 리스크를 최대한 줄이겠다"고 말했다.

인텔도 지난 3월 파운드리 사업 재진출 선언 이후 대규모 투자를 단행하며 TSMC·삼성전자를 맹추격하고 있다. 2024년 2나노에 해당하는 20A(옹스트롬·100억분의 1m), 2025년 1.8나노격인 18A 공정을 적용한 제품 생산을 계획하고 있다. 인텔 역시 20A에서 핀펫 기술을 적용할 예정이다. 하지만 업계는 파운드리 기술 역량이 상대적으로 부족하다고 평가받는 인텔이 삼성전자보다 빠르게 2나노 이하 초미세공정 양산에 성공할 지 의구심을 보이고 있다.

현재 전세계 반도체 제조사 중 10나노 미만 양산 공정을 갖춘 기업은 TSMC와 삼성전자가 유일하다. 반도체업계 관계자는 "인텔은 사실상 한 번도 파운드리 사업을 제대로 해 본 적 없는 기업"이라며 "당초 계획대로 양산이 이뤄질 지는 미지수"라고 말했다.

mkchang@fnnews.com 장민권 기자

※ 저작권자 ⓒ 파이낸셜뉴스, 무단전재-재배포 금지