알파웨이브세미 등과 생태계 구축

초미세공정에 필요한 IP 확보 속도

많은 반도체 설계 IP 보유할수록

고객사 원하는 다양한 칩 생산 가능

초미세공정에 필요한 IP 확보 속도

많은 반도체 설계 IP 보유할수록

고객사 원하는 다양한 칩 생산 가능

19일 관련 업계에 따르면 삼성전자는 차세대 반도체 설계에 필요한 IP 파트너와 협업하며 파운드리 생태계 확장에 나서고 있다. 삼성전자는 시놉시스, 케이던스, 알파웨이브세미 등과 협력해 구축한 반도체 IP 생태계를 2나노 공정까지 넓혔다. 알파웨이브세미는 이날 삼성전자와 전략적 파트너십 확대를 발표하며 5나노(SF5), 4나노(SF4), 2나노(SF2) 등 인공지능(AI), 고성능컴퓨팅(HPC), 자율주행차 등에 탑재되는 초미세공정 반도체에 필요한 IP를 제공하기로 했다. 삼성전자는 지난 2월부터 영국 반도체 IP 기업 ARM의 차세대 시스템온칩(SoC) IP를 자사 게이트올어라운드(GAA) 기반 공정에 적용하는 등 IP 기업들과 협력을 강화하고 있다.

IP는 반도체 기능을 회로로 구현한 설계 블록이다. 반도체 제조 공정 난이도가 기하급수로 올라가는 상황에서 반도체 IP는 파운드리 경쟁력에 직결되는 요소로 꼽힌다. 비용·시간 한계상 모든 IP를 직접 개발하기 어려운 팹리스(반도체 설계전문)는 IP 회사에 라이선스 수수료를 지급하고, 개발된 IP를 사용한다. 팹리스가 설계하는 반도체 칩은 IP 회사가 제공하는 IP를 기반으로 만들어진다. 파운드리 기업 역시 해당 IP를 확보해야 팹리스가 원하는 수준의 칩 생산이 가능해지는 셈이다. 파운드리 1위 기업 TSMC는 삼성전자와 비교해 월등히 많은 IP를 보유한 것으로 전해졌다.

글로벌 파운드리 시장에서 TSMC와의 점유율 격차가 점차 벌어지고 있는 만큼 삼성전자에겐 초미세공정 경쟁력을 높이는 게 최우선 과제다.

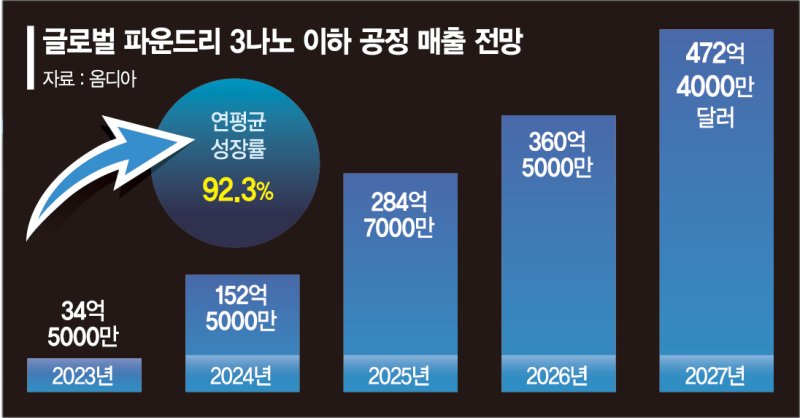

대만 현지 매체 등에 따르면 TSMC는 엔비디아, 애플 등 글로벌 팹리스의 물량을 대거 수주하며 2026년까지 3나노 공정 주문 예약이 모두 끝났다. AI 시대를 맞아 첨단공정 칩 수요가 급증하자 TSMC는 3나노 칩 가격을 5% 인상하는 방안까지 검토하며 시장 지배자로서 자신감을 한껏 드러내고 있다. 반면 삼성전자 파운드리사업부는 팹리스인 시스템LSI사업부와 중국 암호화폐 업체 등을 제외하면 3나노 이하 공정에서 눈에 띄는 대형 고객사가 없다. 글로벌 파운드리 시장에서 3나노 이하 선단공정 매출이 가파르게 증가하는 상황에서 삼성전자 내부에선 TSMC와의 점유율 격차를 반드시 좁혀야 한다는 위기감이 높다. 실제 삼성전자는 최근 메모리·파운드리·패키징을 아우르는 '턴키'(일괄공급) 전략, 후면전력공급(BSPDN) 기술을 적용한 2나노 공개 등에 나서며 고객사 유치에 사활을 걸고 있다.

업계 관계자는 "삼성전자의 TSMC 추격 핵심은 초미세공정 기술 완성도"라며 "다양한 조건의 칩 생산에 필요한 반도체 IP를 폭넓게 확보하고 있는 것도 대형 고객사 신뢰 회복 전략의 일환으로 보인다"고 말했다.

mkchang@fnnews.com 장민권 기자

※ 저작권자 ⓒ 파이낸셜뉴스, 무단전재-재배포 금지